### Problem 1

a) Some of the electrical testing was performed at higher-than-normal temperatures or at higher-than-normal voltages. Why would this testing be performed under such stressful conditions even before the chips, boards, or systems have left the manufacturing area?

Soln:- Such testing leads to failure of weak chips, boards, or systems. This prevents further processing of products that are not of the required quality thus saving time and money.

## b) How SPM can be used to manipulate single atoms?

**Soln:** - Scanning probe microscopy (SPM) uses a probe (instead of light source) to image specimen surfaces. This is done by mechanically moving the probe over the surface. And the resolution depends on the size of the probe. Hence, if the probe is sufficiently small it can be used to manipulate single atoms by selectively charging it.

# c) List at least three different applications of robotics

Soln: - The following are some of the applications of robotics:-

- 1. Industrial manufacturing (e.g. welding, assembly, processing)

- 2. Medicine (e.g. surgical application)

- 3. Surveillance (e.g. disaster zones, hazardous environments, drones, extraterrestrial bodies)

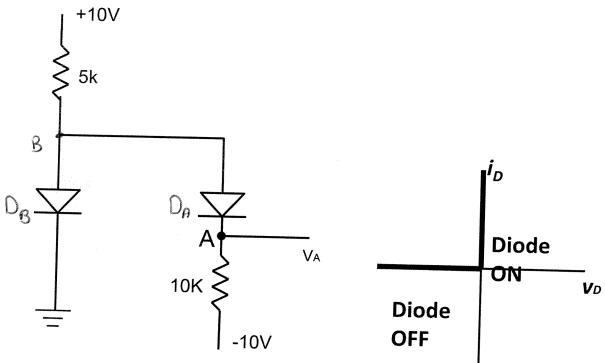

Problem 2 Consider the diode circuit in figure 1 below. The diodes are both ideal. Determine the voltage at point A,  $V_{A\cdot}$

Fig. 1

Diode DB is turned ON, hence vollage at Point B, VB = 0

Similarly diode DA is turned ON, hence voltage at point A, VA = VB = 0 V

### **Problem 3**

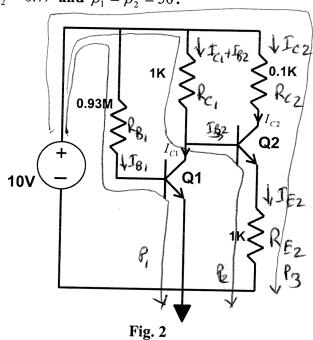

In the circuit shown in Fig. 2, assume that both transistors are operating in active region. Find the collector currents  $I_{C1}$ ,  $I_{C2}$ , and the collector to emitter voltages  $V_{CE1}$ ,  $V_{CE2}$  for both transistors if  $V_{BE1} = V_{BE2} = 0.7V$  and  $\beta_1 = \beta_2 = 50$ .

Applying KVL dong

$$P_{i}$$

$$-10 + I_{B_{i}} \times R_{B_{i}} + V_{BE_{i}} = 0$$

$$I_{B_{i}} = \frac{10 - 0.7}{930 \times 10^{3}} = 10 \text{ MA}$$

$$I_{C_{i}} = \beta * I_{B_{i}} = \frac{500 \text{ MA}}{930 \times 10^{3}}$$

$$EVL along P_{2}$$

$$-10 + (I_{C_{i}} + I_{B_{2}})R_{C_{i}} + V_{BE_{2}} + I_{E_{2}} * R_{E_{2}} = 0$$

$$-10 + 0.5 + 0.7 + I_{B_{2}} * R_{e_{i}} + (\beta + 1)I_{B_{2}} * R_{E_{3}} = 0$$

$$I_{B_{2}} = (R_{c_{1}} + 51 * R_{E_{2}}) = 8.8$$

$$I_{B_{2}} = 8.5 \text{ mA}$$

$$I_{C_{2}} = \beta * I_{B_{2}} = 8.5 \text{ mA}$$

$$V_{c_1} = 10 - (1_{c_1} + 1_{B_2}) * K_{c_1}$$

$V_{c_1} = 10 - (500 + 169.2) * 10^6 * R_{c_1}$

$V_{c_1} = 9.33 Y$

$V_{c_{c_1}} = V_{c_1} = 9.33 Y$

Applying KVL along

$$P_3$$

$I_{E2} = I_{C2} + I_{B2} = 8 - 669 \text{ mA}$

$I_{E2} = I_{C2} + I_{B2} = 8 - 669 \text{ mA}$

$I_{E2} = I_{E2} + I_$

### Problem 4

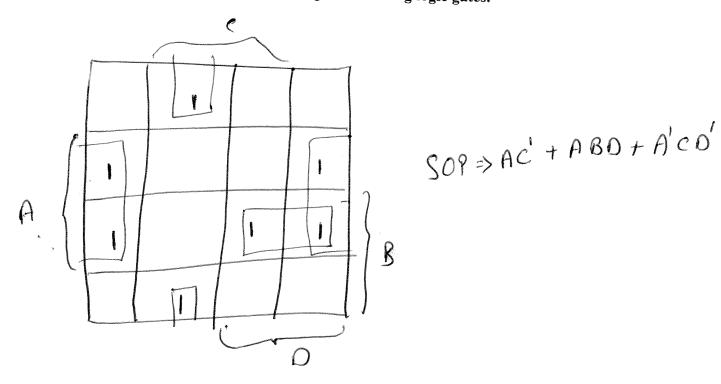

a) Use Karnaugh map to obtain the minimum SOP (sum of product) form for the following Boolean function:

$$Z = ABC'D' + AB'C'D' + ABC'D + AB'C'D + ABCD + A'B'CD' + A'BCD'$$

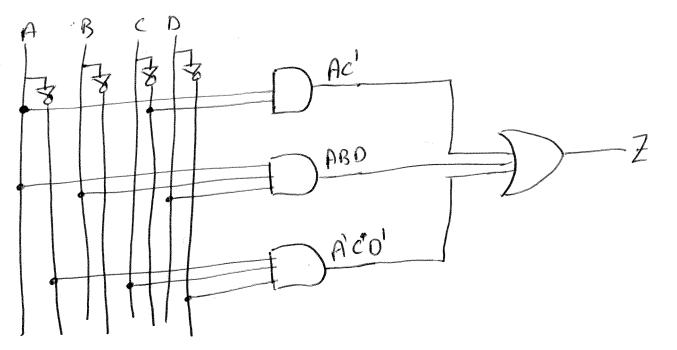

b) Then implement the minimum SOP expression using logic gates.

Problem 5

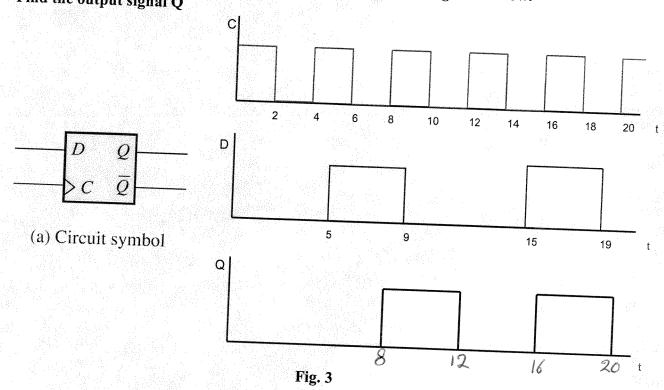

The input D to a positive-edge triggered flip-flop is shown in figure 3 below. Find the output signal Q